一种基于功耗管理的DSP处理器设计

一种具有功耗管理特性的DSP处理器的结构设计.该处理器采用4级流水线和增强型的哈佛并行系统结构及完善的时钟管理模块,提供了一种DSP处理器的集成设计方案.能很好地满足便携式数字信号处理系统中要求的信号高速处理能力和良好的功耗特性.

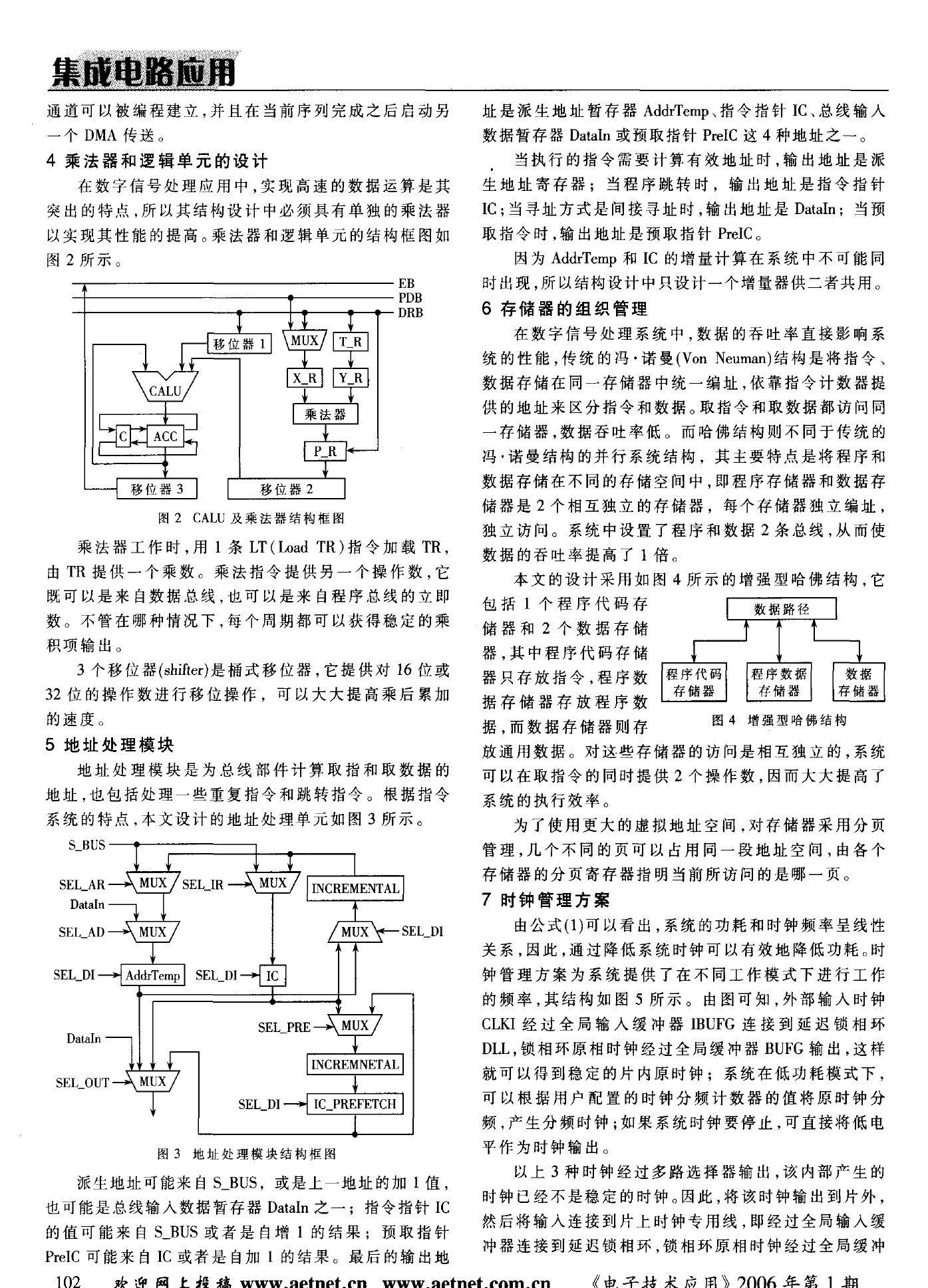

一种基于功耗管理的DSP处理器设计李钊辉(西北工业大学软件-9微电子学院,陕西西安710065)摘要:一种具有功耗管理特性的DSP处理器的结构设计。该处理器采用4级流水线和增强型的哈佛并行系统结构及完善的时钟管理模块,提供了一种DSP处理器的集成设计方案。能很好地满足便携式数字信号处理系统中要求的信号高速处理能力和良好的功耗特性。关键词:DSP处理器流水线哈佛结构低功耗在信息日益成为一种重要资源的今天,强大的市场器地址,并取出指令。需求和微电子技术的发展促成了便携式电子系统的飞速DI:译码阶段。通过指令译码产生相应的微控制信发展。这些便携式电子设备,不但对速度和面积要求非号,送人相应的控制寄存器。常高,而且对系统的平均功耗要求也很严格,使功耗问题FO:+取操作数阶段。从寄存器堆或外部存储器读出日渐成为制约便携式电子设备发展的瓶颈。要获得高性相应的数据,通过数据总线送入运算单元或寄存器堆。能低功耗的方案,其实质也就是在处理速度、芯片面积EXE/WB:执行及写回阶段。进行运算或操作,得出和功耗上来权衡如何满足数字信号处理系统的要求。相应的结果,并将结果