CPLD设计的驱动数码显示电路

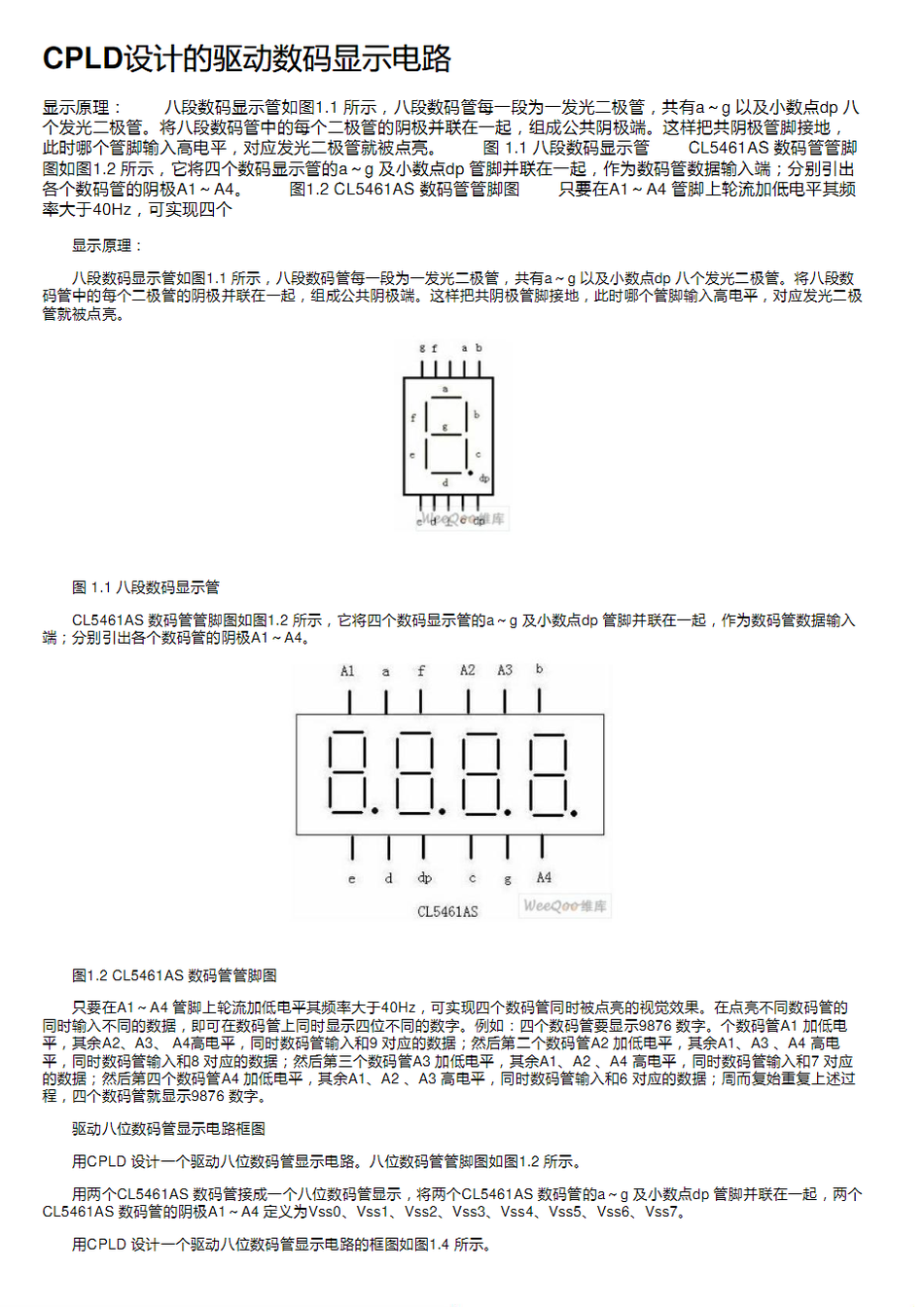

显示原理: 八段数码显示管如图1.1 所示,八段数码管每一段为一发光二极管,共有a~g 以及小数点dp 八个发光二极管。将八段数码管中的每个二极管的阴极并联在一起,组成公共阴极端。这样把共阴极管脚接地,此时哪个管脚输入高电平,对应发光二极管就被点亮。 图 1.1 八段数码显示管 CL5461AS 数码管管脚图如图1.2 所示,它将四个数码显示管的a~g 及小数点dp 管脚并联在一起,作为数码管数据输入端;分别引出各个数码管的阴极A1~A4。 图1.2 CL5461AS 数码管管脚图 只要在A1~A4 管脚上轮流加低电平其频率大于40Hz,可实现四个