如何使用Verilog编写同步RAM

在FPGA设计实现中,经常要用到RAM,这里的RAM一般指的是静态的RAM。一般FPGA(如xilinx)中就有所谓的blockRAM,它就是现成的RAM资源,通过合理编写verilog代码,RAM可以被综合成blockRAM,从而节省逻辑资源,提高性能。在FPGA设计中,同步RAM的使用至关重要,尤其是在高性能、低延迟的应用中。同步RAM以单个时钟信号为同步基准,确保数据读写操作的正确性和一致性。Verilog是一种硬件描述语言,便于设计者创建这类存储器结构。本篇详细讲解如何使用Verilog编写同步RAM,并探讨其在FPGA中的实现和优化。

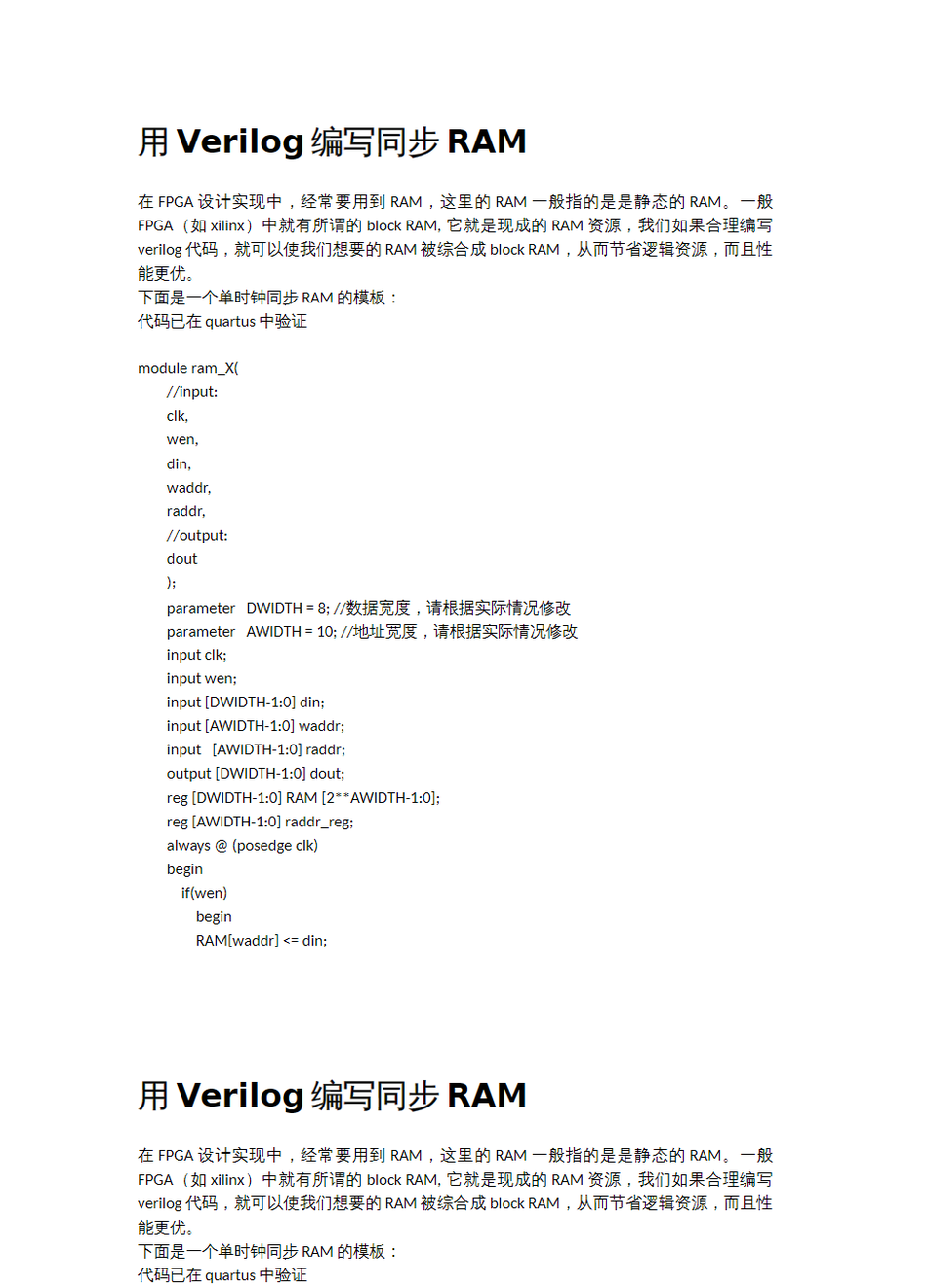

同步RAM通常由两个主要部分组成:写入模块和读取模块。写入模块在时钟上升沿接收数据和地址信号,更新存储单元;读取模块在同一时钟边沿读取指定地址的数据。在Verilog中,可以使用always块来实现这些功能。以下是一个简单的同步RAM模板,适用于Xilinx FPGA中的block RAM资源:

module ram_X( input clk, input wen, input [DWIDTH-1:0] din, input [AWIDTH-1:0] waddr, input [AWIDTH-1:0] raddr, output [DWIDTH-1:0] dout );

parameter DWIDTH = 8;

parameter AWIDTH = 10;

input clk;

input wen;

input [DWIDTH-1:0] din;

input [AWIDTH-1:0] waddr;

input [AWIDTH-1:0] raddr;

output [DWIDTH-1:0] dout;

reg [DWIDTH-1:0] RAM [2**AWIDTH-1:0];

reg [AWIDTH-1:0] raddr_reg;

always @(posedge clk) begin

if(wen) begin

RAM[waddr] <;= din;

end

end

always @(posedge clk) begin

raddr_reg <;= raddr;

end

assign dout = RAM[raddr_reg];

endmodule

在这个模板中,DWIDTH参数定义了RAM的数据宽度,AWIDTH定义了地址宽度。wen是写使能信号,waddr和dout分别是写入地址和数据,raddr是读取地址,dout是输出数据。

为了优化设计,还可以考虑:

-

双端口RAM:支持同时进行读写操作。

-

突发读写:提高数据传输效率。

-

错误检测和校验:提高数据可靠性。

-

初始化和预加载:在FPGA配置时预先加载RAM内容。