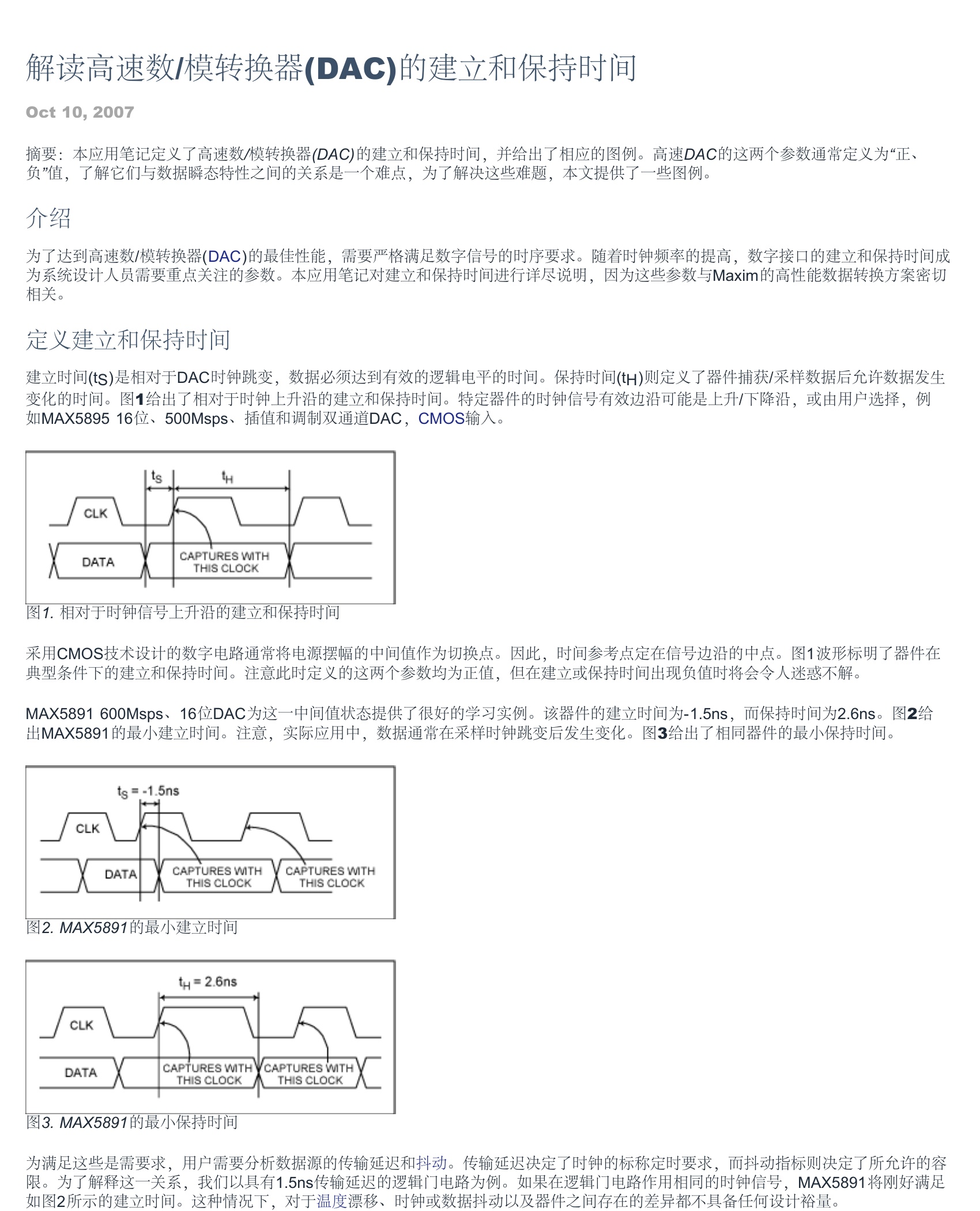

摘要:本应用笔记定义了高速数/模转换器(DAC)的建立和保持时间,并给出了相应的图例。高速DAC的这两个参数通常定义为“正、负”值,了解它们与数据瞬态特性之间的关系是一个难点,为了解决这些难题,本文提供了一些图例。解读高速数/模转换器(DAC)的建立和保持时间Oct10,2007摘要:本应用笔记定义了高速数/模转换器(DAC)的建立和保持时间,并给出了相应的图例。高速DAC的这两个参数通常定义为“正、负”值,了解它们与数据瞬态特性之间的关系是一个难点,为了解决这些难题,本文提供了一些图例。介绍为了达到高速数/模转换器(DAC)的最佳性能,需要严格满足数字信号的时序要求。随着时钟频率的提高,数字接口的建立和保持时间成为系统设计人员需要重点关注的参数。本应用笔记对建立和保持时间进行详尽说明,因为这些参数与Maxim的高性能数据转换方案密切相关。定义建立和保持时间建立时间(tS)是相对于DAC时钟跳变,数据必须达到有效的逻辑电平的时间。保持时间(tH)则定义了器件捕获/采样数据后允许数据发生变化的时间。图1给出了相对于时钟上升沿的建立和保持时间。特定器件的时钟信号有效边沿可能是上升/下降沿,或由用户选择,例如MAX589516位、500Msps、插值和调制双通道DAC,CMOS输入。图1.相对于时钟信号上升沿的建立和保持时间采用CMOS技术设计的数字电路通常将电源摆幅的中间值作为切换点。因此,时间参考点定在信号边沿的中点。图1波形标明了器件在典型条件下的建立和保持时间。注意此时定义的这两个参数均为正值,但在建立或保持时间出现负值时将会令人迷惑不解。MAX5891600Msps、16位DAC为这一中间值状态提供了很好的学习实例。该器件的建立时间为-1.5ns,而保持时间为2.6ns。图2给出MAX5891的最小建立时间。注意,实际应用中,数据通常在采样时钟跳变后发生变化。图3给出了相同器件的最小保持时间。图2.MAX5891的最小建立时间图3.MAX5891的最小保持

暂无评论