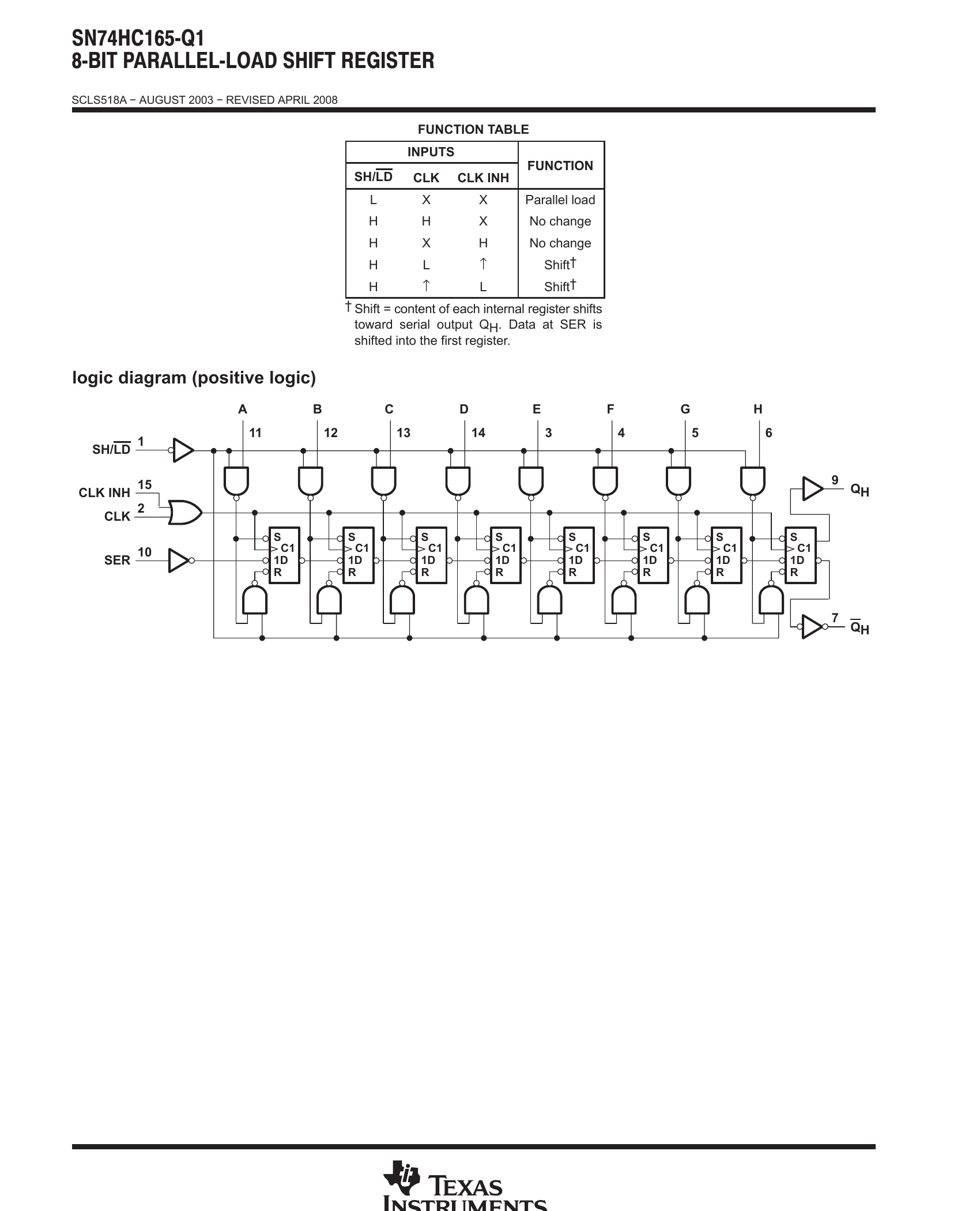

The SN74HC165 is an 8-bit parallel-load shift register that, when clocked, shift the data toward a serial (QH) output. Parallel-in access to each stage is provided by eight individual direct data (A-H) inputs that are enabled by a low level at the shift/load (SH/LD) input. The SN74HC165 also features a clock-inhibit (CLK INH) funcTIon and a complementary serial (QH) output.

Clocking is accomplished by a low-to-high transiTIon of the clock (CLK) input while SH/LD is held high and CLK INH is held low. The funcTIons of CLK and CLK INH are interchangeable. Since a low CLK and a low-to-high transiTIon of CLK INH also accomplish clocking, CLK INH should be changed to the high level only while CLK is high. Parallel loading is inhibited when SH/LD is held high. While SH/LD is low, the parallel inputs to the register are enabled independently of the levels of the CLK, CLK INH, or serial (SER) inputs.

暂无评论