74LS374中文资料:54/74374

八上升沿 D 触发器(3S,时钟输入有回环特性)

简要说明:

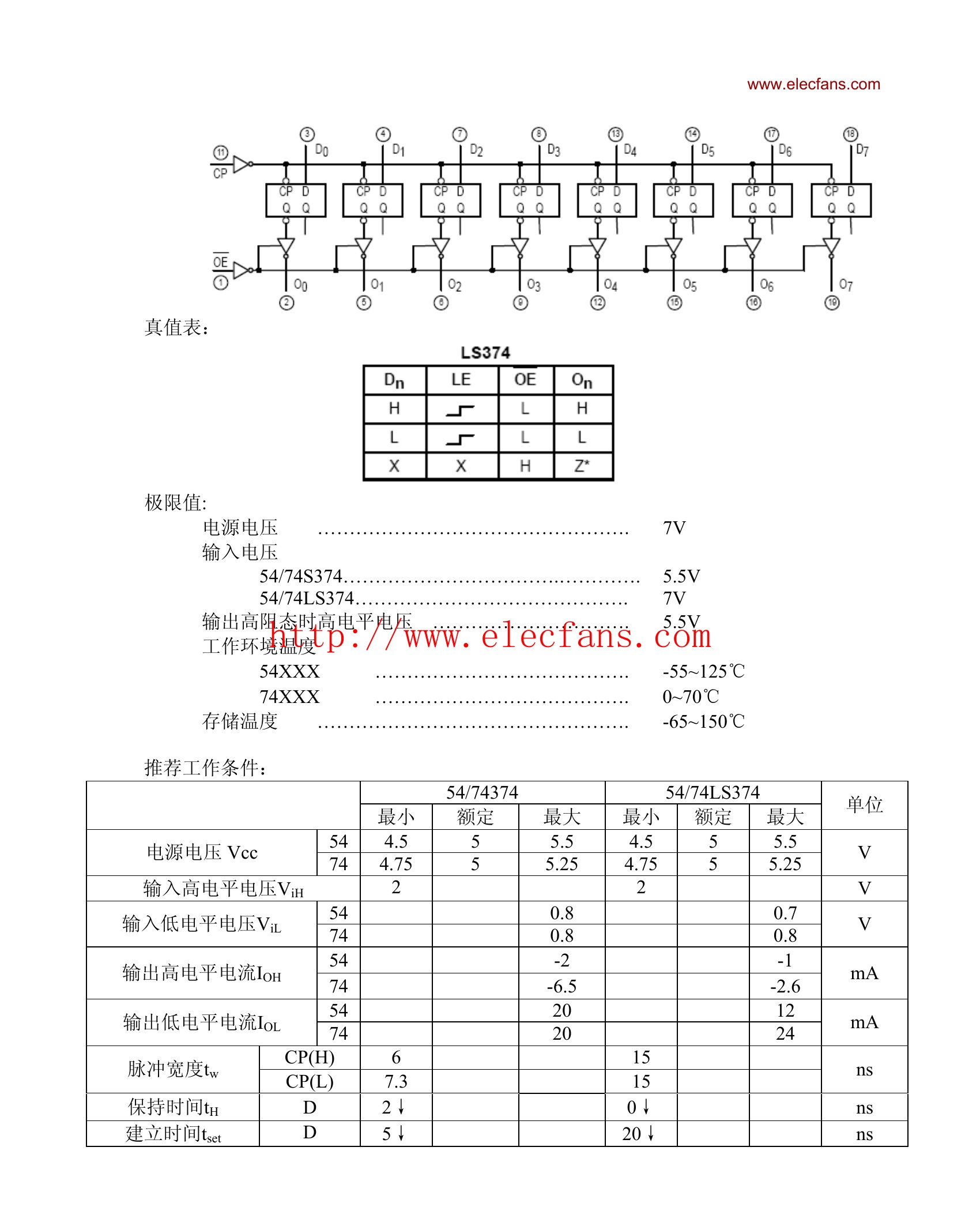

374为具有三态输出的八 D 边沿触发器,共有 54/74S374 和 54/74LS374 两种

线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):

型号 fm PD

54S374/74S374 100MHz 450mW

54LS374/74LS374 50MHz 135mW

374 的输出端 O0~O7 可直接与总线相连。当三态允许控制端 OE 为低电平时,

O0~O7 为正常逻辑状态,可用来驱动负载或总线。当 OE 为高电平时,O0~O7 呈

高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当时钟端 CP 脉冲上升沿的作用下,O 随数据 D 而变。

由于 CP 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善

400mV。

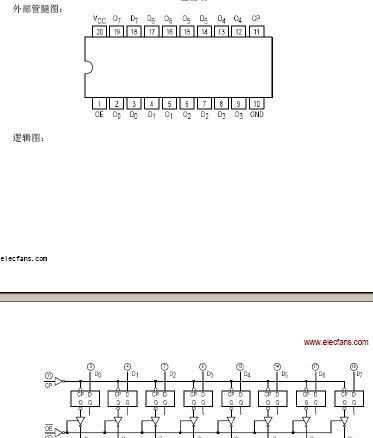

引出端符号:

D0~D7 数据输入端

OE 三态允许控制端(低电平有效)

CP 时钟输入端

O0~O7 输出端

外部管腿图:逻辑图:真值表:

暂无评论