在新的信号链和模数转换器(ADC)前端设计中,系统设计人员需要考虑许多前端拓扑结构和设计权衡因素。

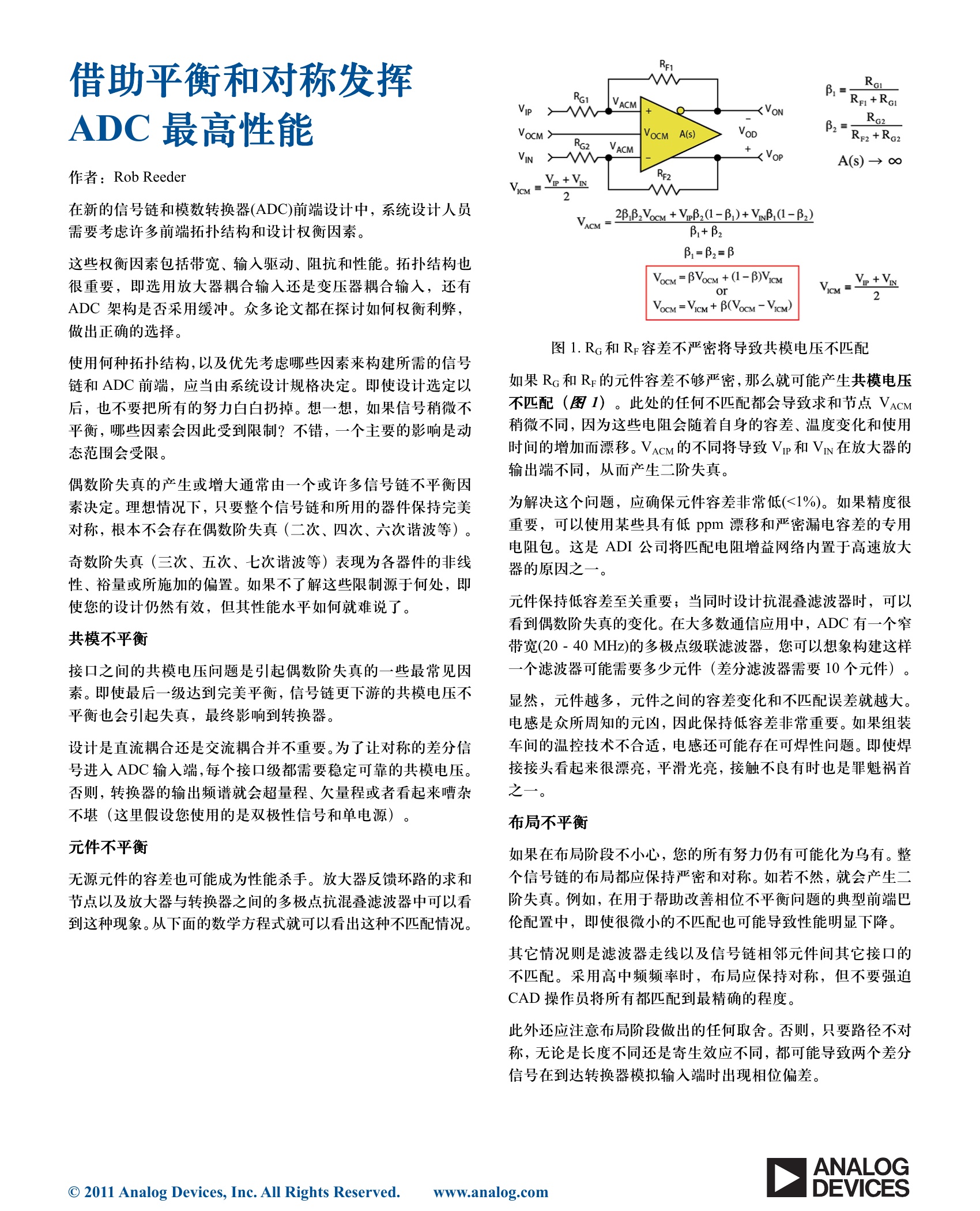

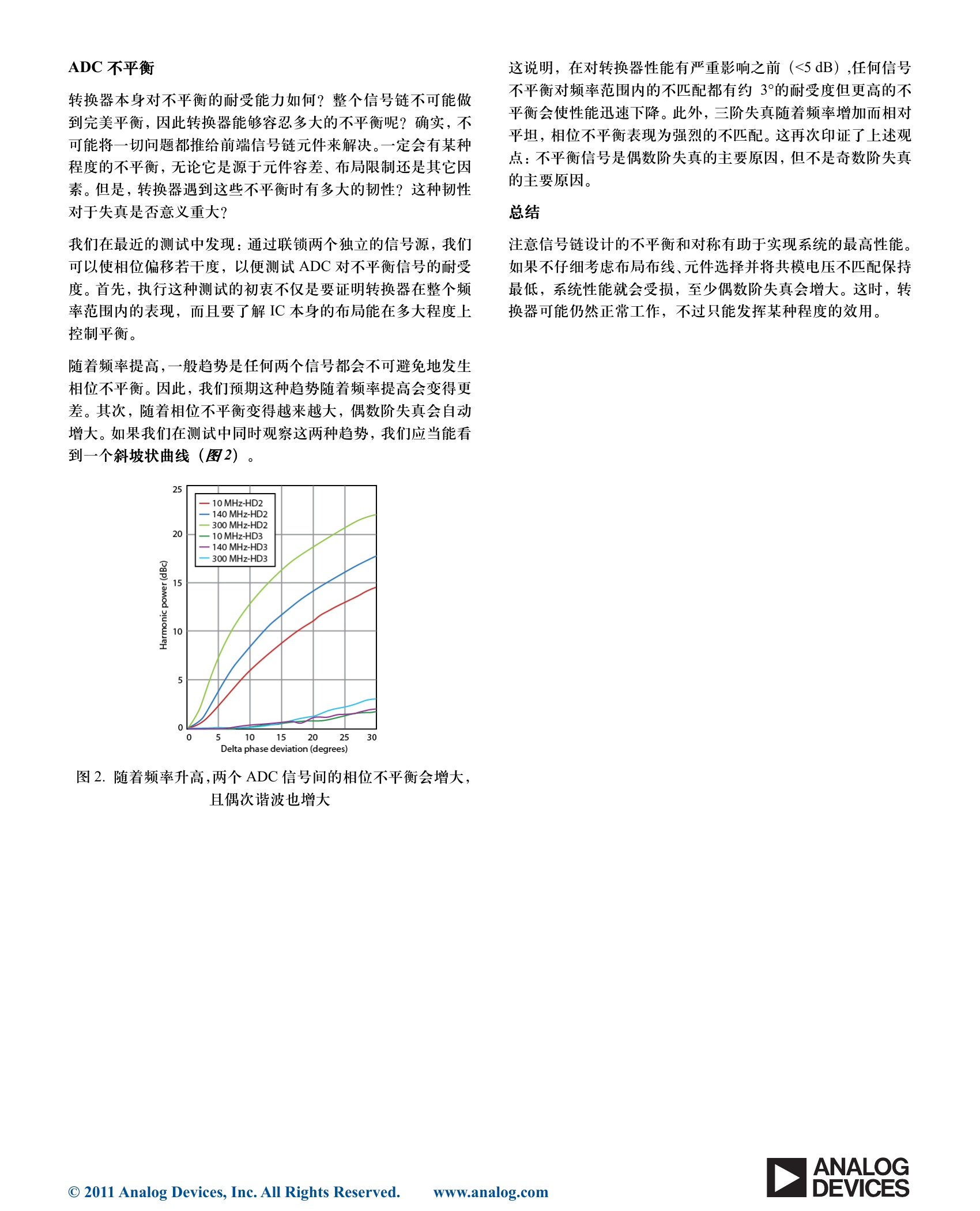

这些权衡因素包括带宽、输入驱动、阻抗和性能。拓扑结构也很重要,即选用放大器耦合输入还是变压器耦合输入,还有ADC架构是否采用缓冲。众多论文都在探讨如何权衡利弊,做出正确的选择。借助平衡和对称发挥ADC最高性能作者:RobReeder在新的信号链和模数转换器(ADC)前端设计中,系统设计人员需要考虑许多前端拓扑结构和设计权衡因素。这些权衡因素包括带宽、输入驱动、阻抗和性能。拓扑结构也很重要,即选用放大器耦合输入还是变压器耦合输入,还有ADC架构是否采用缓冲。众多论文都在探讨如何权衡利弊,做出正确的选择。图1.RG和RF容差不严密将导致共模电压不匹配使用何种拓扑结构,以及优先考虑哪些因素来构建所需的信号链和ADC前端,应当由系统设计规格决定。即使设计选定以如果RG和RF的元件容差不够严密,那么就可能产生共模电压后,也不要把所有的努力白白扔掉。想一想,如果信号稍微不不匹配(图1)。此处的任何不匹配都会导致求和节点VACM平衡,哪些因素会因此受到限制?不错,一个主要的影响是动稍微不同,因为这些电阻会随着自身的容差、温度变化和使用态范围会受限。时间的增加而漂移。VACM的不同将导致VIP和VIN在放大器的输出端不同,从而产生二阶失真。偶数阶失真的产生或增大通常由一个或许多信号链不平衡因素决定。理想情况下,只要整个信号链和所用的器件保持完美为解决这个问题,应确保元件容差非常低(<1%)。如果精度很对称,根本不会存在偶数阶失真(二次、四次、六次谐波等)。重要,可以使用某些具有低ppm

暂无评论