FPGA_CPLD数字电路设计经验分享.pdf

摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。

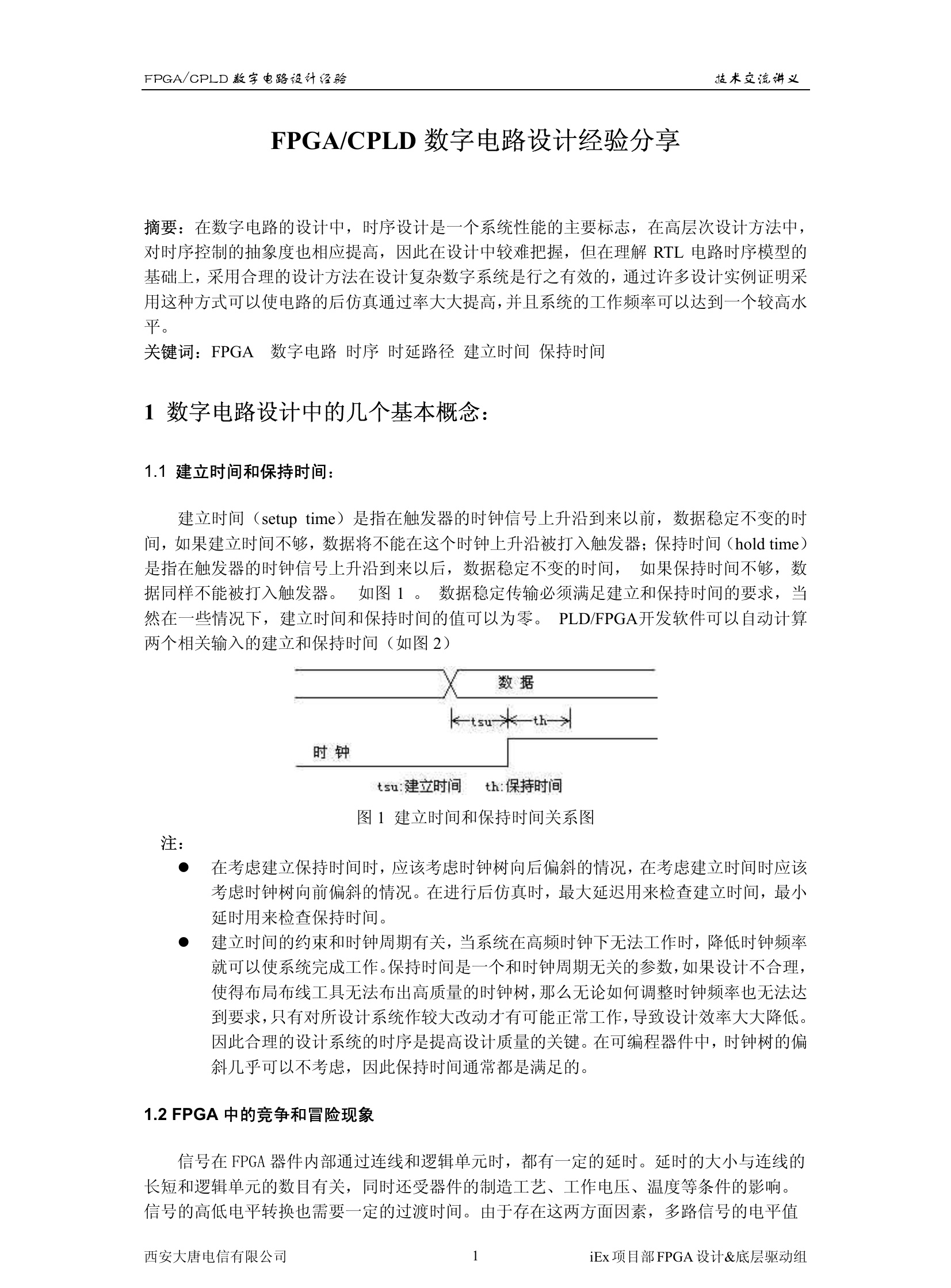

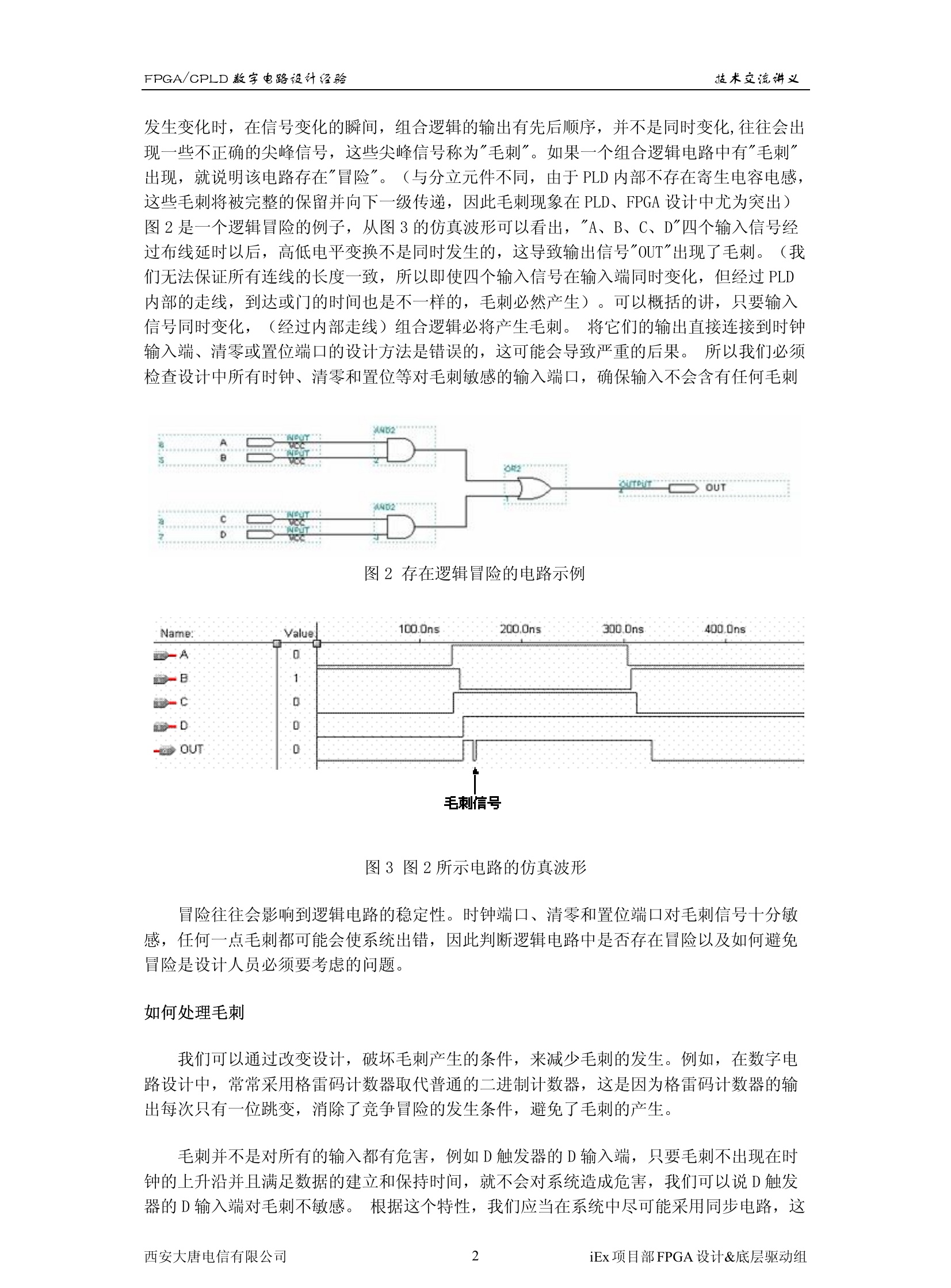

关键词:FPGA数字电路时序时延路径建立时间保持时间FPGA/CPLD数字电路设计经验技术交流讲义FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。关键词:FPGA数字电路时序时延路径建立时间保持时间1数字电路设计中的几个基本概念:1.1建立时间和保持时间:建立时间(setuptime)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(holdtime)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。如图1。数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间(如图2)图1建立时间和保持时间关系图注:在考虑建立保持时间时,应该考虑时钟树向后偏斜的情况,在考虑建立时间时应该考虑时钟树向前偏斜的情况。在进行后仿真时,最大延迟用来检查建立时间,最小延时用来检查保持时间。建立时间的约束和时钟周期有关,当系统在高频时钟

暂无评论