TheInter-IC(I

2

C)busisatwo-wireserialinterface

developedbyPhilips/Signetics.Thespecificationsup-

portsdatatransmissionupto400Kbps.

TheI

2

Cinterfaceemploysacomprehensiveprotocolto

ensurereliabletransmissionandreceptionofdata.

Whenthebusisactive,onedeviceistheMaster

(generatestheclockandthehandshakingsignals),

whilealltheotherdevicesareSlaves.Thecurrentbus

Mastercanbothread-fromandwrite-toanyoftheSlave

unitsbyaddressingthemindividually.OnaMulti-Mas-

terbustheMastersfollowanarbitrationschemeto

ensurethatthebusisnotcorrupted.

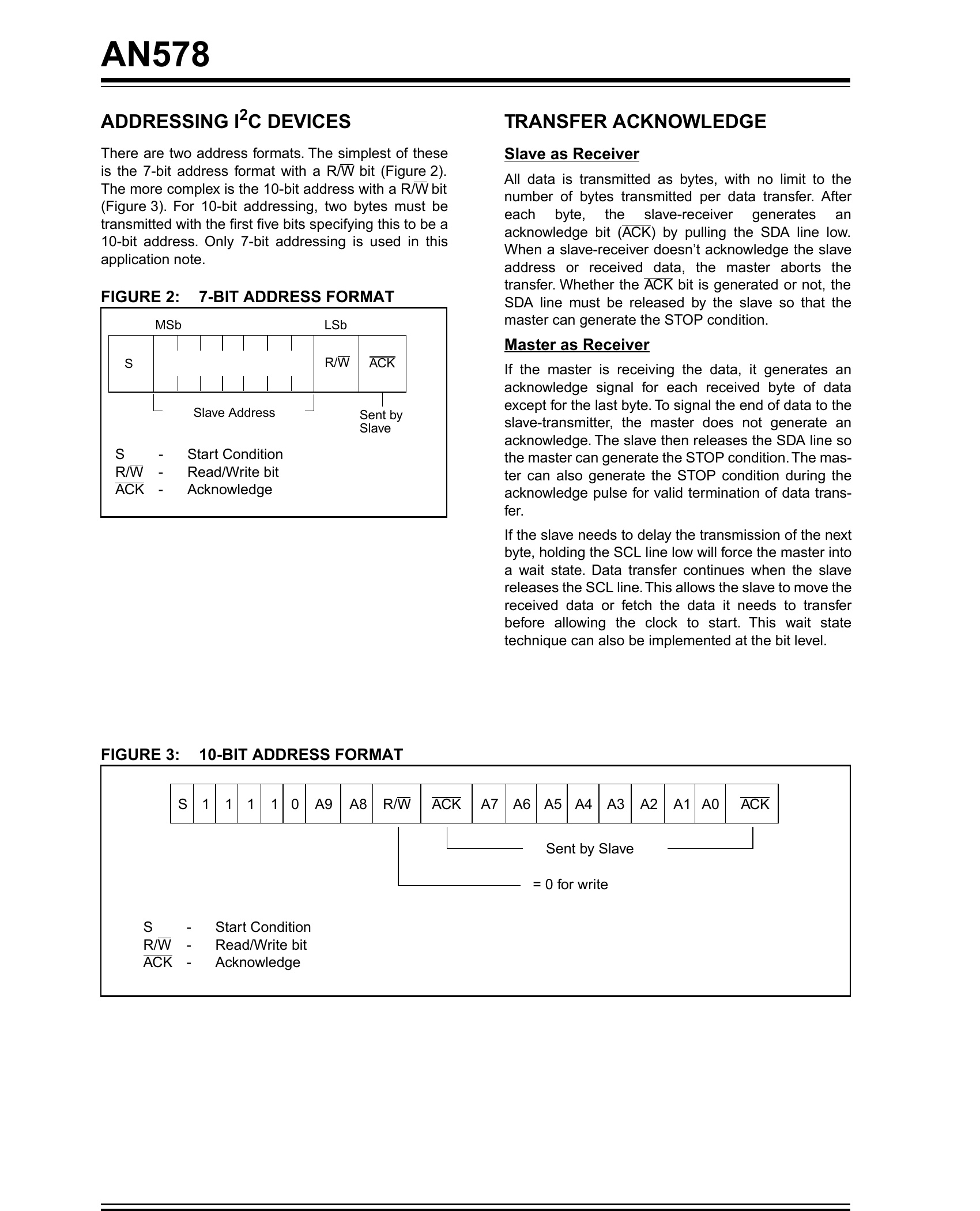

EachdeviceattachedtotheI

2

Cbusisassigneda

uniqueaddress.WhenaMasterwishestoinitiatea

datatransfer,itfirsttransmitstheaddressofthedevice

thatitwishesto“talk”to.Alldevices“listen”toseeifthis

istheiraddress.Withinthisaddress,abitspecifies

whethertheMasterwishestoread-fromorwrite-tothe

Slavedevice.

Theoutputstagesofeachdeviceonthebus,attached

totheclock(SCL)anddata(SDA)lines,musthavean

open-drainoropen-collectorinordertoperformthe

wired-ANDfunctionofthebus.Externalpull-up

resistorsareusedtoensureahighlevelwhenno

deviceispullingthelinedown.Theonlylimitationon

thenumberofdevicesthatmaybeattachedtothebus

isthemaximumbusloadingspecification.Forcomplete

busspecifications,refertoPhilips/Signeticsdocument

“TheI

2

C-busandHowtoUseIt”(www.semiconduc-

tors.philips.com).MUseoftheSSPModuleintheI2CMulti-MasterEnvironmentAN578INITIATINGANDTERMINATINGAuthor:ScottFinkMicrochipTechnologyInc.DATATRANSFERDuringtimesofnodatatransfer(idletime),boththeINTRODUCTIONSCLandSDAlinesarepulledhigh.AMasterdevicewhichwishestotakecontrolofthebusmustrstgen-TheInter-IC(I2C)busisatwo-wireserial

暂无评论