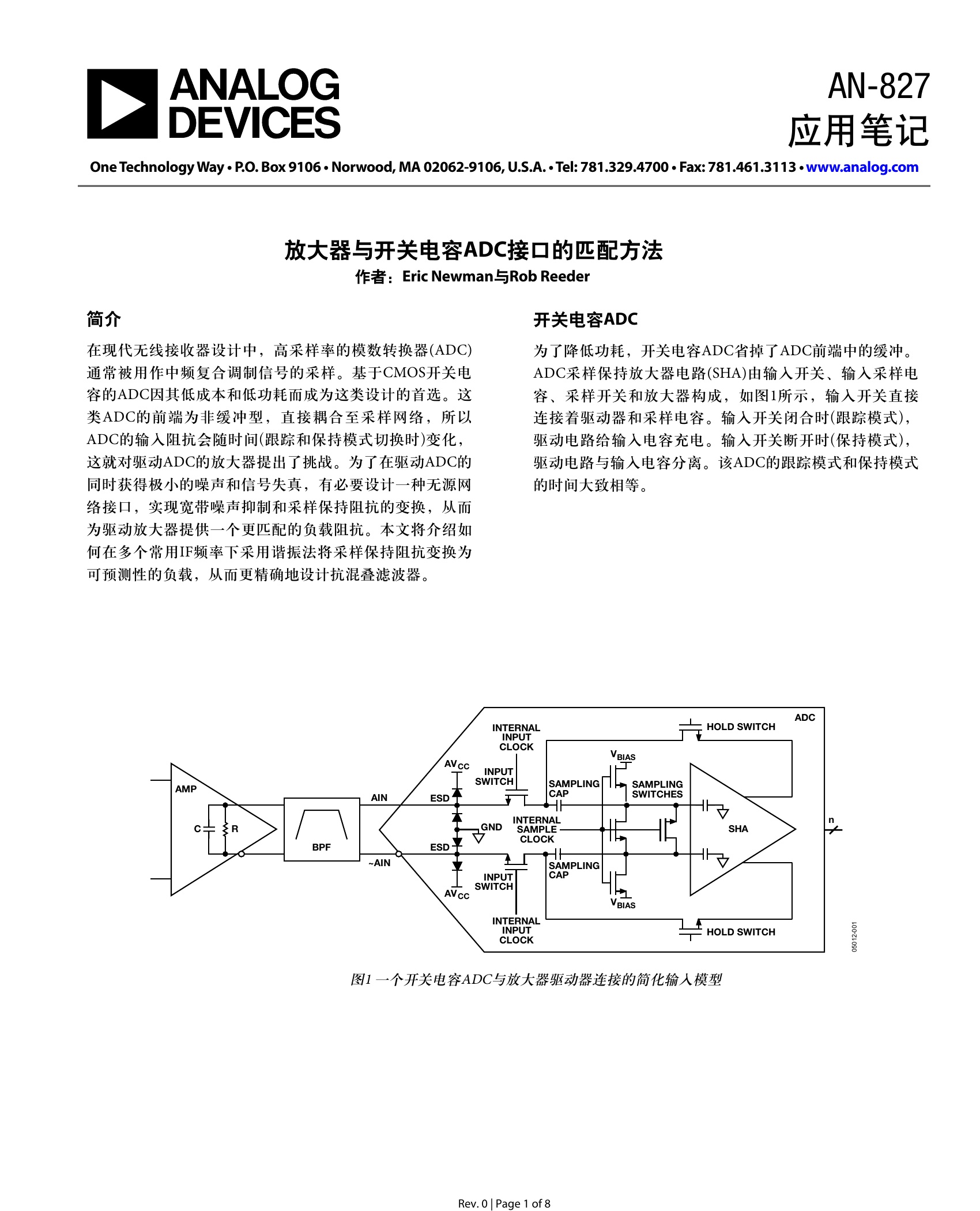

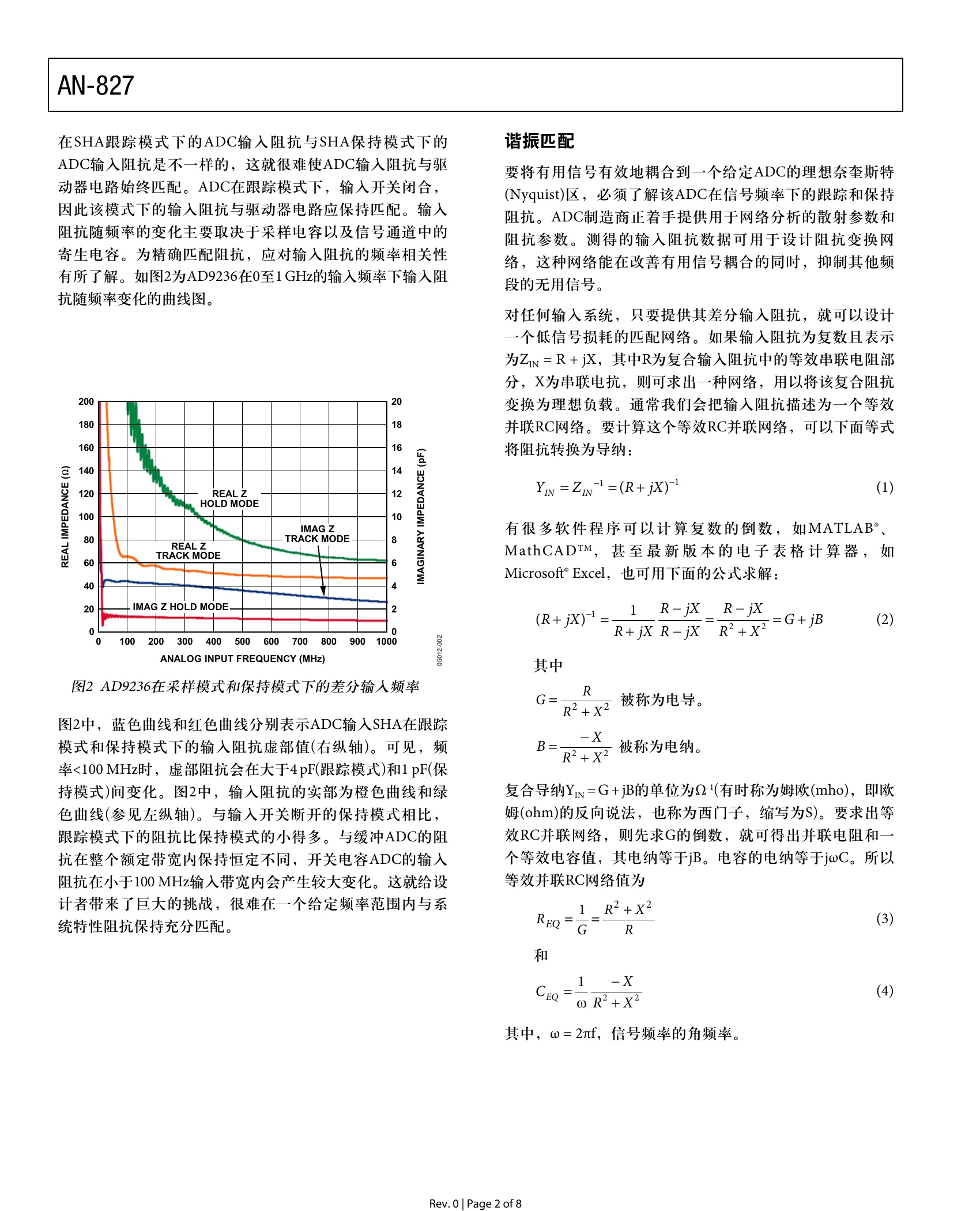

简介在现代无线接收器设计中,高采样率的模数转换器(ADC)通常被用作中频复合调制信号的采样。基于CMOS开关电容的ADC因其低成本和低功耗而成为这类设计的首选。这类ADC的前端为非缓冲型,直接耦合至采样网络,所以ADC的输入阻抗会随时间(跟踪和保持模式切换时)变化,这就对驱动ADC的放大器提出了挑战。为了在驱动ADC的同时获得极小的噪声和信号失真,有必要设计一种无源网络接口,实现宽带噪声抑制和采样保持阻抗的变换,从而为驱动放大器提供一个更匹配的负载阻抗。本文将介绍如何在多个常用IF频率下采用谐振法将采样保持阻抗变换为可预测性的负载,从而更精确地设计抗混叠滤波器。开关电容ADC为了降低功耗,开关电容ADC省掉了ADC前端中的缓冲。ADC采样保持放大器电路(SHA)由输入开关、输入采样电容、采样开关和放大器构成,如图1所示,输入开关直接连接着驱动器和采样电容。输入开关闭合时(跟踪模式),驱动电路给输入电容充电。输入开关断开时(保持模式),驱动电路与输入电容分离。该ADC的跟踪模式和保持模式的时间大致相等。AN-827应用笔记One Technology WayP.O.Box9106Norwood,MA02062-9106,U.S.A.Tel:781.329.4700Fax:781.461.3113www.analog.com放大器与开关电容ADC接口的匹配方法作者:Eric Newman与Rob Reeder简介开关电容ADC在现代无线接收器设计中,高采样率的模数转换器(ADC)为了降低功耗,开关电容ADC省掉了ADC前端中的缓冲。通常被用作中频复合调制信号的采样。基于CMOS开关电ADC采样保持放大器电路(SHA)由输入开关、输入采样电容的ADC因其低成本和低功耗而成为这类设计的首选。这容、采样开关和放大器构成,如图1所示,输入开关直接类ADC的前端为非缓冲型,直接耦合至采

暂无评论