噪声对高性能模拟电路设计人员来说是一个极其重要的参

数。对高速时钟、模数转换器 (ADC)、数模转换器

(DAC)、电压控制振荡器(VCO)和锁相环(PLL)来说尤其如

此。降低输出电压噪声的关键是保持交流闭环增益接近单

位增益,且不影响交流性能和直流闭环增益。

本应用笔记描述如何用简单的RC网络降低可调低压差稳压

器(LDO)的输出噪声。我们将提供针对多个LDO的实验数

据,以展示这一简单电路技术的有效性。尽管降噪(NR)是

本应用笔记的重点,但同时一些测试数据也展示了降噪对

电源抑制比(PSRR)和瞬变负载响应的影响。

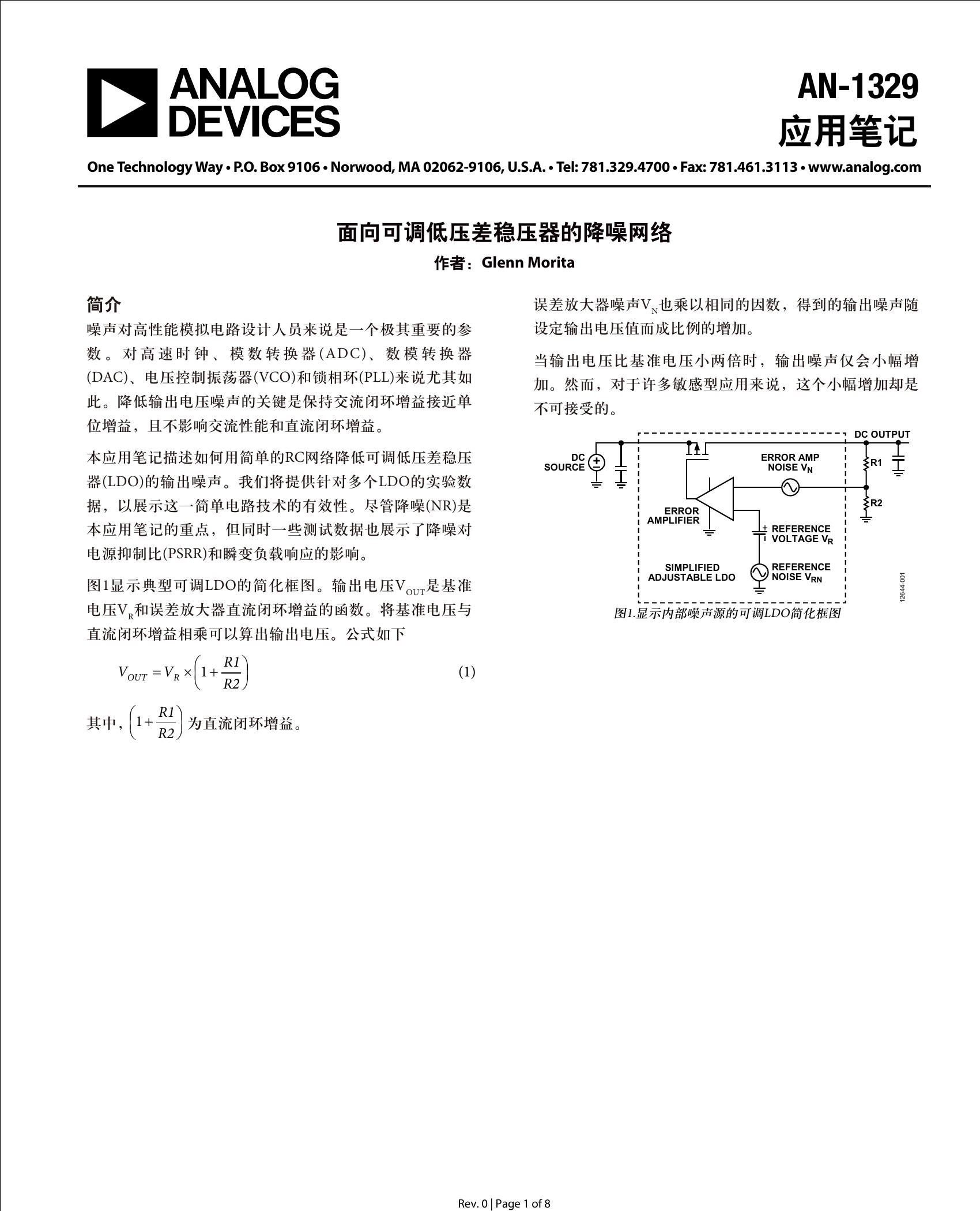

图1显示典型可调LDO的简化框图。输出电压VOUT是基准

电压VR和误差放大器直流闭环增益的函数。将基准电压与

直流闭环增益相乘可以算出输出电压。公式如下

误差放大器噪声VN也乘以相同的因数,得到的输出噪声随

设定输出电压值而成比例的增加。

当输出电压比基准电压小两倍时,输出噪声仅会小幅增

加。然而,对于许多敏感型应用来说,这个小幅增加却是

不可接受的

暂无评论