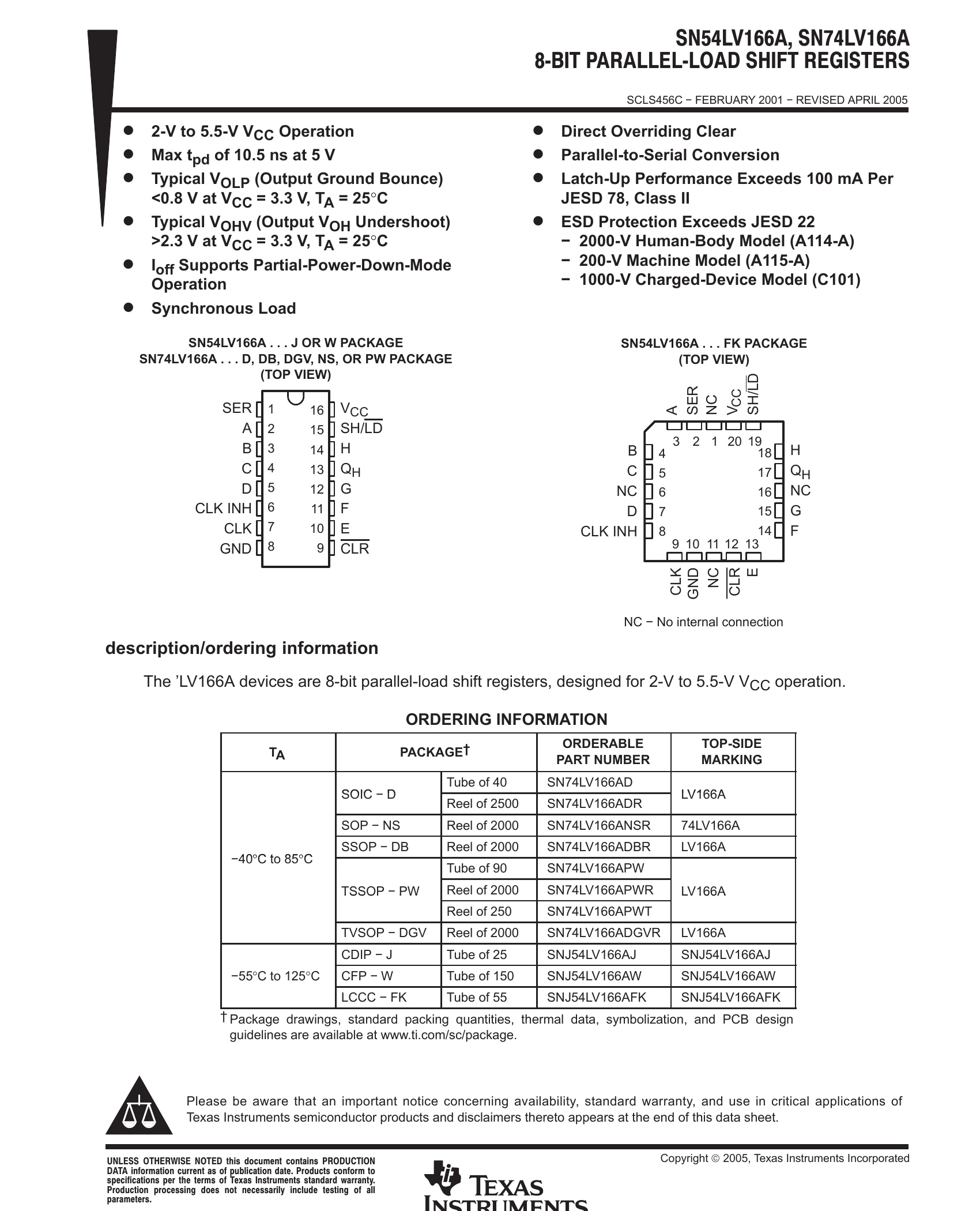

The 'LV166A devices are 8-bit parallel-load shift registers, designed for 2-V to 5.5-V VCC operaTIon.

The 'LV166A parallel-in or serial-in, serial-out registers feature gated clock (CLK, CLK INH) inputs and an overriding clear (CLR\) input. The parallel-in or serial-in modes are established by the shift/load (SH/LD\) input. When high, SH/LD\ enables the serial (SER) data input and couples the eight flip-flops for serial shifTIng with each clock (CLK) pulse. When low, the parallel (broadside) data inputs are enabled, and synchronous loading occurs on the next clock pulse. During parallel loading, serial data flow is inhibited. Clocking is accomplished on the low-to-high-level edge of CLK through a 2-input posiTIve-NOR gate, permitTIng one input to be used as a clock-enable or clock-inhibit function.

暂无评论