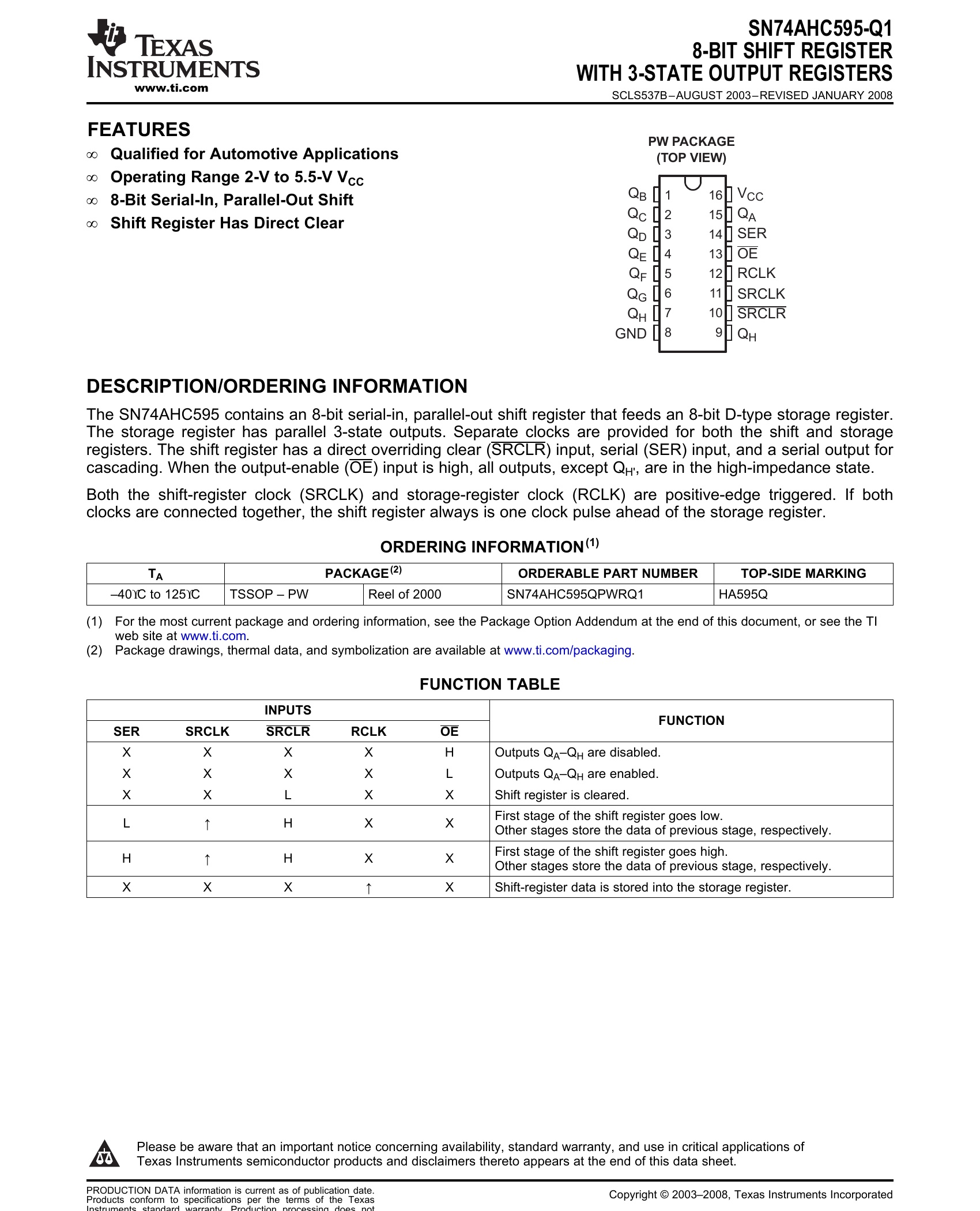

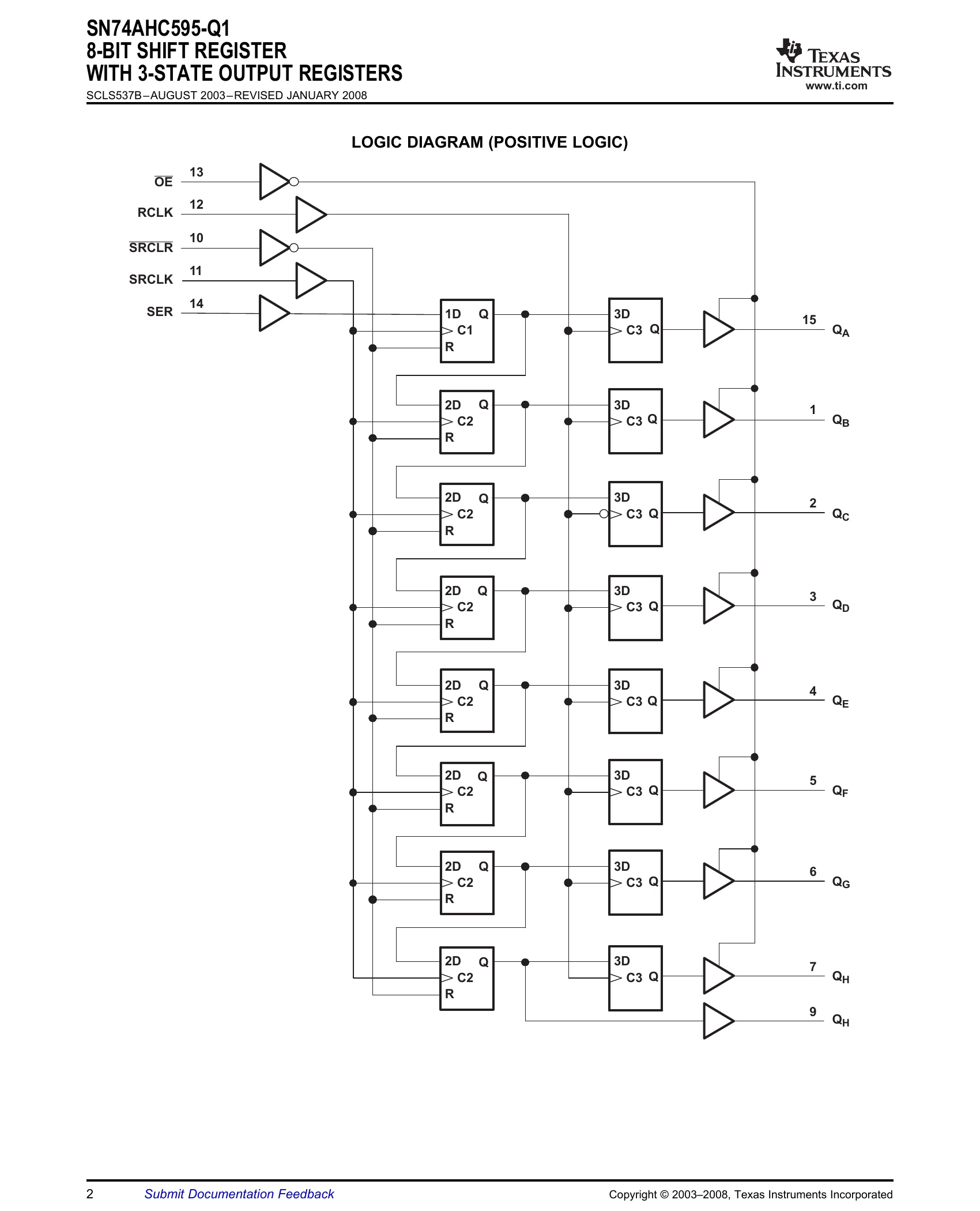

The SN74AHC595 contains an 8-bit serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. The storage register has parallel 3-state outputs. Separate clocks are provided for both the shift and storage registers. The shift register has a direct overriding clear (SRCLR) input, serial (SER) input, and a serial output for cascading. When the output-enable (OE) input is high, all outputs, except QH', are in the high-impedance state.

Both the shift-register clock (SRCLK) and storage-register clock (RCLK) are posiTIve-edge triggered. If both clocks are connected together, the shift register always is one clock pulse ahead of the storage register.

暂无评论