PhaseLockedLoop(PLL)circuitsareincreasingly

usedinmicrocontrollerstoachievehigherinternal

clockfrequencies.Thisallowsbetterperformance

whilereducingoverallnoise.SeveralofMicrochip’s

PIC18microcontrollersfeature4xPLLsintheirclock

generationcircuits.Thismakesitpossibletogenerate

aninternal40MHzclockfromanexternal10MHz

crystal.

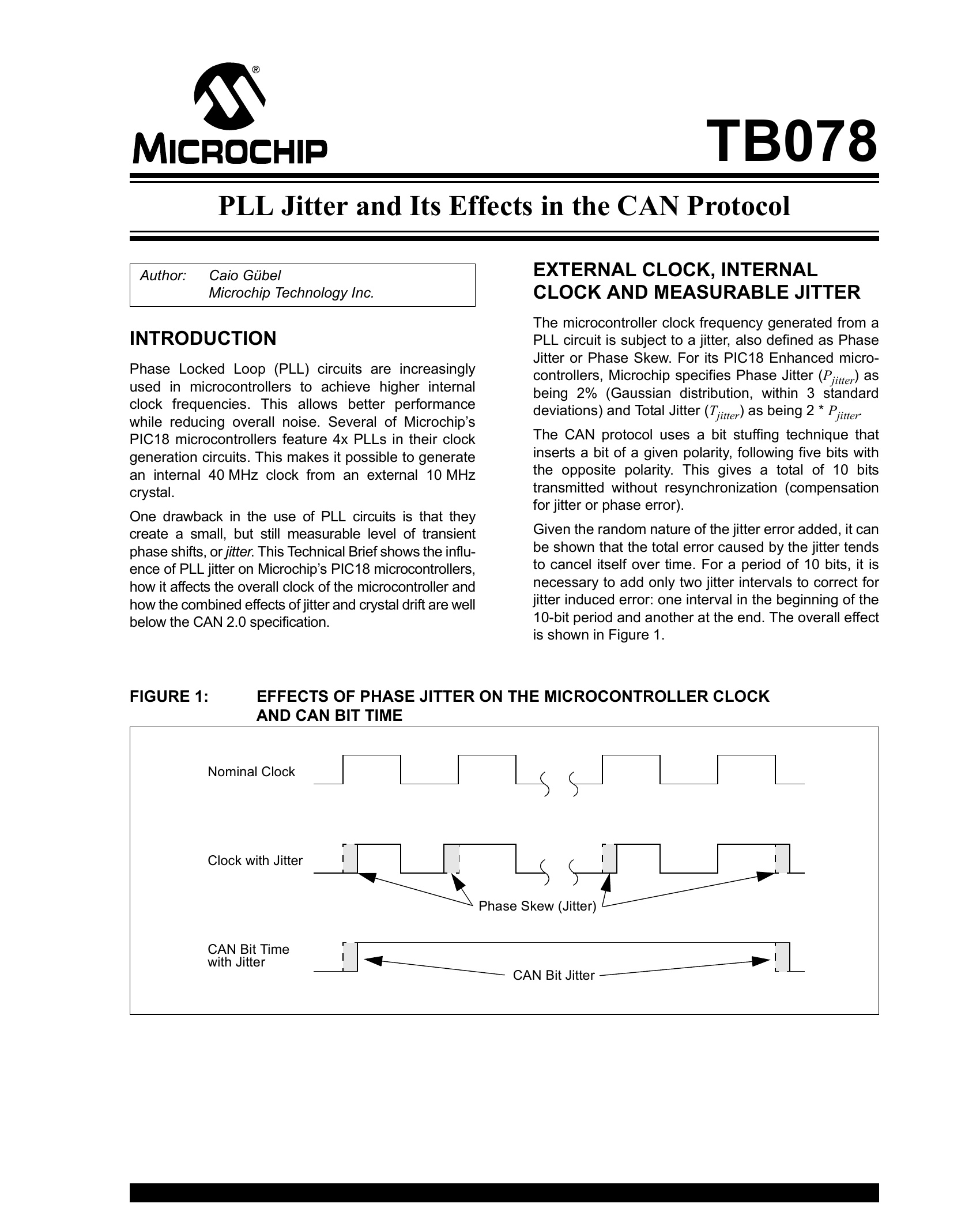

OnedrawbackintheuseofPLLcircuitsisthatthey

createasmall,butstillmeasurableleveloftransient

phaseshifts,orjitter.ThisTechnicalBriefshowstheinflu-

enceofPLLjitteronMicrochip’sPIC18microcontrollers,

howitaffectstheoverallclockofthemicrocontrollerand

howthecombinedeffectsofjitterandcrystaldriftarewell

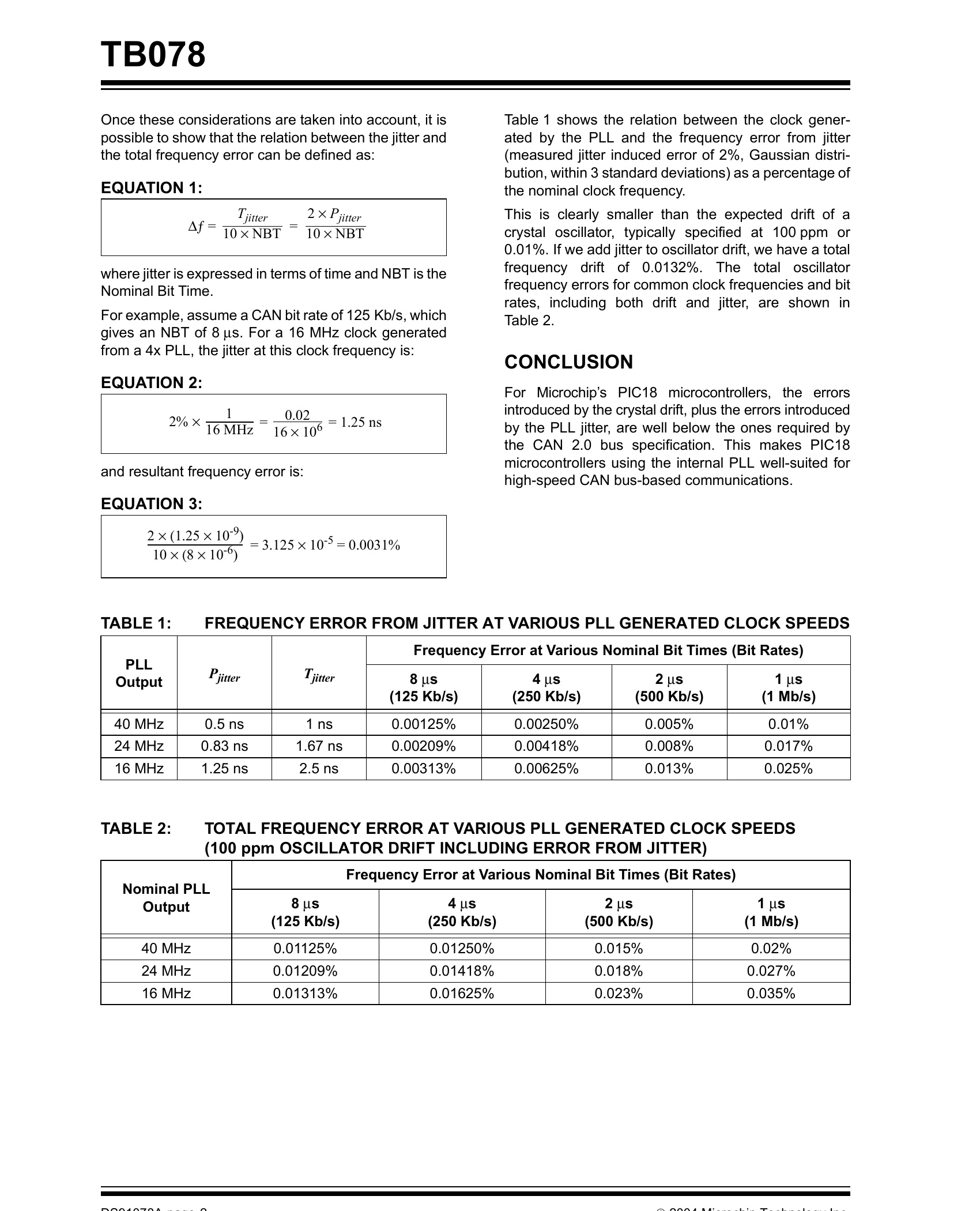

belowtheCAN2.0specification.TB078PLLJitterandItsEffectsintheCANProtocolAuthor:CaioGübelEXTERNALCLOCK,INTERNALMicrochipTechnologyInc.CLOCKANDMEASURABLEJITTERThemicrocontrollerclockfrequencygeneratedfromaINTRODUCTIONPLLcircuitissubjecttoajitter,alsodefinedasPhaseJitterorPhaseSkew.ForitsPIC18Enhancedmicro-PhaseLockedLoop(PLL)circuitsareincreasingly

暂无评论