西南交大数电实验之可控分频器设计

1、 FPGA 开发板上有一个 50MHz 的高频时钟。设计一个可控分频器,clk_in 为分频器

时钟输入,sel为选择开关,clk_out为分频器信号输出。当sel=0时,

fclk_out=sn[3:0]Hz;

当 sel=1 时,fclk_out=sn[4:0] Hz。

2、 clk_out 的占空比 D=20%;(D=tH/T,tH 为高电平时间,T 为周期)

3、 说明。sn 为学号,sn[3:0]表示取十进制学号的后 4 位,sn[4:0]表示取十进制学号的

后 5 位,若学号后 4 位为 0 则学号后 5 位按 32768 取值。例如,学号 sn=2017112345,

sn[3:0]=2345;sn=2017100000,sn[3:0]=2768.

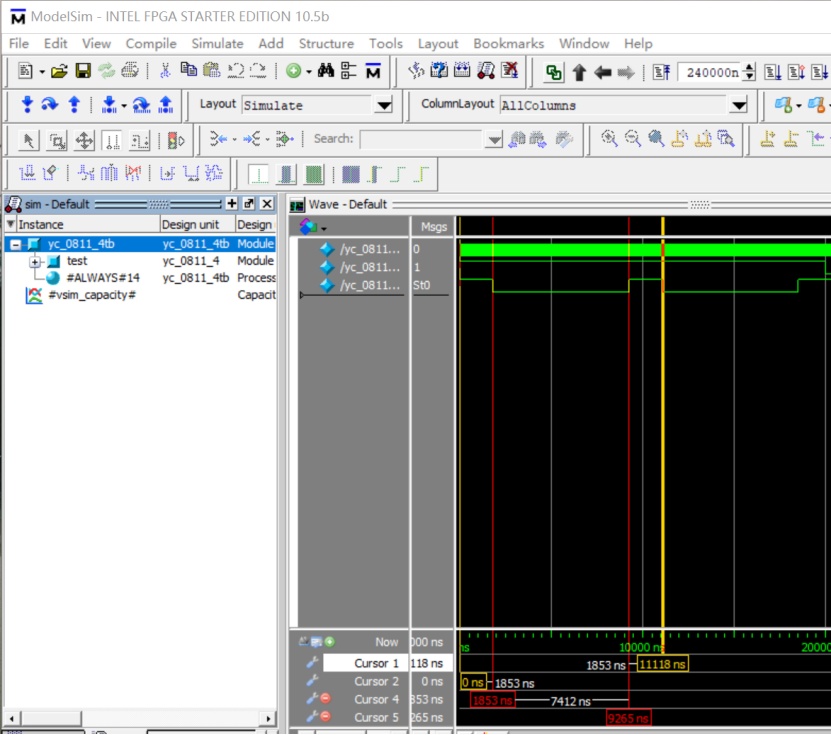

4、 实验测试

5、 用导线将 clk_out 接入实验箱的 CH0 逻辑分析仪通道,测试 clk_out 实际输出频率

及占空比,若与要求不相符(误差须小于 1%),修改电路程序使之符合要求。

暂无评论